The Ultimate Guide to CPLD

02/02/2020, hardwarebee

This article discusses the Complex Programmable Logic Devices (CPLD) history, CPLD family types, CPLD architecture, CPLD clock, and CPLD applications.

When it comes to programmable logic devices or PLDs, there are a number of different options to choose from. From PALs and PLAs, to CPLDs and FPGAs- you can go either way depending on what your individual requirements are in regards to your development project.

What is CPLD?

CPLD stands for Complex Programmable Logic Device. As explained by the name, these are devices with relatively higher complexity than the likes of PALs but are less complex than FPGAs or Field Programmable Gate Arrays.

A CPLD is essentially made up of numerous macrocells, consisting of disjunctive standard form expressions and other logic operations for more specific applications for logic implementation. Macrocells can be defined as the functional unit or building block of a Complex Programmable Logic Device which can perform combinational or sequential logic. They contain a combination of AND and OR gates arranged in an array that can be programmed to perform and execute many different logic functions.

The CPLDs was the forerunner of the FPGA and is still helpful today in several applications. We will start this article to examine the historical development of the CPLD to understand the advantages and disadvantages of the CPLDs. Most major PLD vendors, including Intel (formerly Altera), Xilinx, offer a wide-ranging of complex programmable devices Starting from the most straightforward version name PAL, which is a result of a sum of products (SOP) logic functions using a programmable gate and fixed array of gates followed by a fixed or array. This permitted the substitution of up to a different logic package with a generic logic solution.

CPLD Architecture

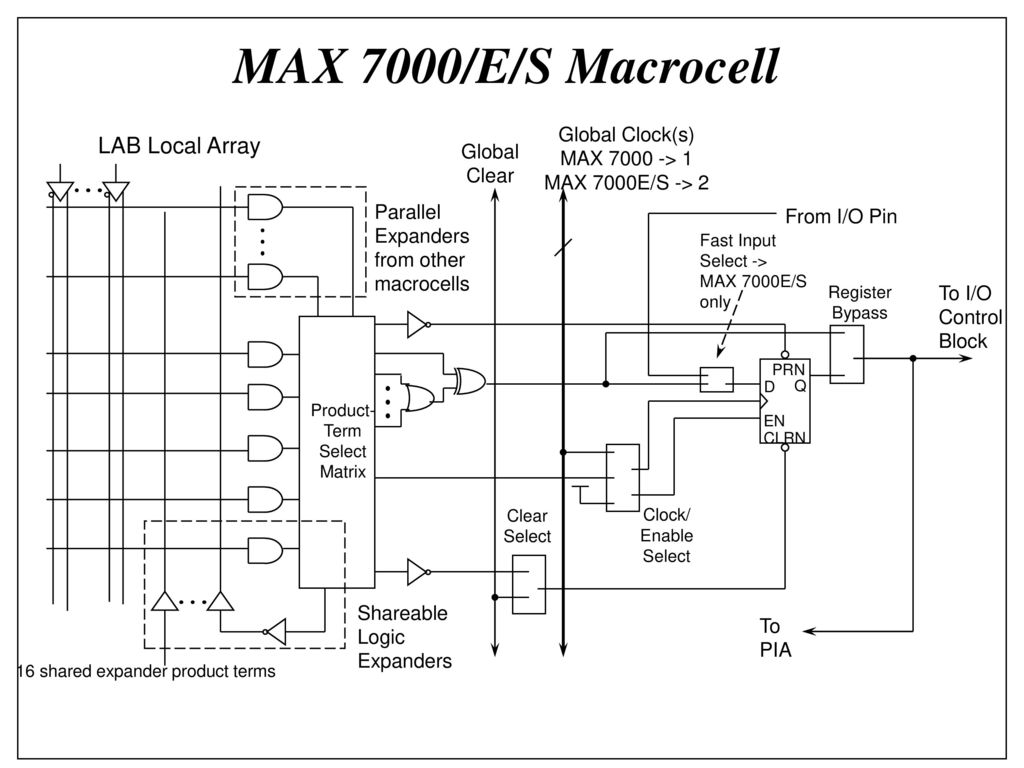

Intel expanded the concept of PAL by putting multiple PAL structures called macrocells into a single unified circuit package in which all the input pins are accessible to each macrocell, and any macrocell could push any output pin. CPLDs were also built-in CMOS technology to be reprogrammable while Bi-polar PALs are not. Although it didn’t seem to be a general characteristic at the time, reprogrammability is now considered a vital aspect of PLD devices. The program that defined the interconnections and CPLDs is stored in an on-chip EE prompt. Intel extended this concept by putting various macrocells in a single IC package in which all the input pins are available to each macrocell, and each macrocell has a devoted output pin. With the capability to explore 16 digital inputs at a time, each macrocell could decode a 16-bit address from a processor and generate a chip select, as shown in Figure below. In this way, a single chip with 8 or 16 macrocells could create tip selects for an entire microprocessor system. The CPLDs are correlated with the processor system’s glue logic.

The above figure shows that a CPLD Macrocell is just essentially a registered PAL array. The fake symbols represent programmable configuration switches present in the device. The PIA is a matrix of interconnecting wires that links the macrocells together, feeding the output of the cells to the inputs of other cells. This arrangement is suitable for the kind of problems that require a good deal of logic for every flip-flop, like a complex sixteen state machine wider-input decoder. However, the CPLD architecture did not scale effectively for designs that required many flip flips. This has become the jurisdiction of the FPGA.

CPLD Family

There are two leading CPLD families: Xilinx (AMD) and Altera (Intel). Starting from Xilinx’s CPLD family, the CPLDs are defined based on the different number of blocks and different I/O blocks.

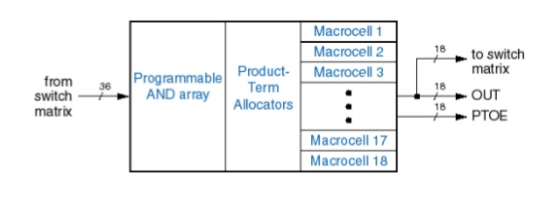

The Figure above shows the functional block of the CPLD Xilinx series XC9500 that contains 18 macrocells per FB, 36 input per FB; macrocell outputs can go to I/O cells or back into the switch matrix to be routed to this.

Intel-Altera has the series name MAX for the CPLDs starting from MAX – 10, MAX – V, MAX – II. They provide the lowest power, lowest cost CPLDs. MAX V CPLD family, the newest family in the CPLD series, delivers the market’s best value. Featuring unique, non-volatile architecture and one of the industry’s largest density CPLDs, MAX V devices provide a robust design.

CPLD Features

There are several features that CPLDs possess that makes them similar to other chips and devices in their category and set them apart as a unique solution that is the optimum choice for specific scenarios and situations based on the user’s requirements. Here are some of the most important and defining features of CPLDs:

- CPLDs have a relatively large number of gates that implement more complex devices and programs possible. Compared to PALs, which generally have gates ranging around a couple of hundred, CPLDs have thousands to over tens of thousands of gates.

- Special logic functions, as well as complex interconnected feedback paths between the macro cells, makes CPLD logic much more flexible and modifiable as compared to others.

- CPLD does not require an external configuration memory and can start operating immediately after the system has been booted up. It is a type of non-volatile configuration memory.

- They employ the use of Electrically Erasable Programmable Read-Only Memory (EEPROM).

- Thanks to the non-volatile and non-ROM based configuration of the CPLDs, you do not have to worry about any unexpected delays or memory loss. The memory is retained in the circuit even when it has been powered down.

- CPLDs are also easy to reprogram at a meagre cost, reducing your overall costs and expenditure while simultaneously improving the time to market of your products.

- The integrative and simplistic nature of CPLDs makes them a perfect fit in most design flows and architecture, posing very little trouble in terms of integration and design adjustments.

- They have low maintenance costs, proving to be a sound investment in the long run.

- The non-volatile nature of CPLDs makes them a much more secure option as it is next to impossible to steal the stored design. The external memory of the FPGA devices can expose the IP, although the user can implement encryption techniques to combat this security threat.

- CPLDs are much better suited for deterministic timing analysis than FPGAs because of a lesser number of interconnects.

In some cases, you may find that both. CPLDs and FPGAs can be used and implemented together for optimum performance and functioning. In these designs, CPLDs are typically dedicated to acting as glue logic, and they also boot up the FPGA and the rest of the board.

CPLD Clock

CPLD requires multiple clocks because several parts of the CPLD will be programmed with separate functionality that operates asynchronously from other parts of the CPLD using different clock domains.

Some clocks will be generated from the external clock source using one of the unique clocks generating chips that generated different clocks that have defined phase relationships. These can be leveraged in different sections of the CPLD to improve the functioning performance of the chip programming.

It is perfectly safe to have different parts of the CPLD using different clocks. Your task as the designer is to use intense care to keep each circuit restricted to its clock domain. And, if it turns out to be essential for some logic to make a crossing from one clock domain to another, you apply the necessary design consistency to apply the essential clock synchronization circuits to the crossing paths to confirm that the consequential logic is stable and not issue to metastability problems.

CPLD Applications

The applications of CPLDs include the following:

- They for high performance, critical control applications.

- Used for boot loader

- Used as a memory element

- Used for address decoding

- CPLDs used for small logic calculations or checksum generation

CPLD vs. FPGA- The Differences Between Them

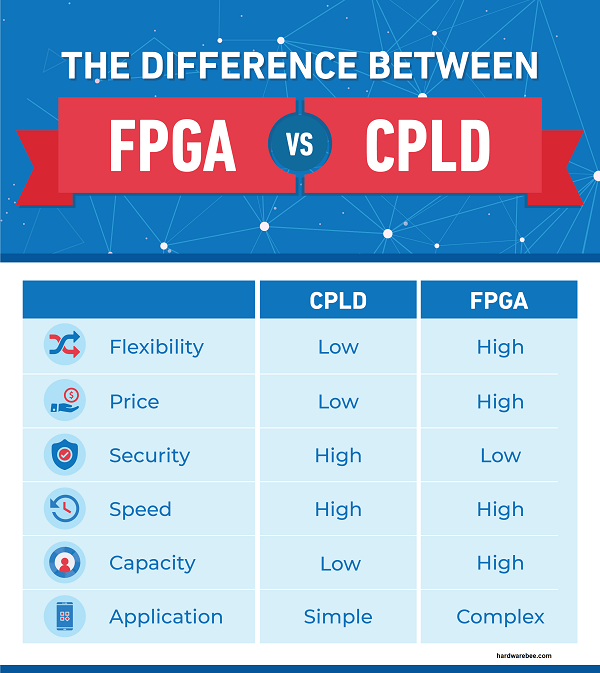

FPGAs can essentially be considered as a more advanced or even more complex version of CPLDs. The primary difference between them is that where CPLDs use a sum of products logic with a sea of gates, FPGA uses internal look up tables or LUTs.

FPGAs can accommodate for millions of gates and also offer much more flexibility thanks to their field modifiable circuit design. Compared to CPLDs, FPGAs are RAM based and lose their memory and data when the power source is removed. This means that you will need to download the data and the configuration from an external memories source to begin its operation again. This can, unfortunately, lead to boot up delays which you will not encounter with the non volatile CPLDs. FPGAs are also more expensive when considered as an overall package.

Between CPLDs and FPGAs, it is wiser to go with the former if you are making simple applications. Go with the latter for more complex applications. CPLDs used to be known for their high power consuming modules, but the latest versions and models have turned it around and have been made much more efficient in terms of power use and dissipation. Thermal management, however, still remains a prominent issue in high complexity and high speed FPGAs. As mentioned before, another problem with FPGAs is that the complex network of interconnected between the various function blocks causes less deterministic signal routing. Because of this, timing scenarios become complicated and implementation tools need to be provided to the user by the vendor to allow for deterministic timing of signals.

In some cases, you may find that both. CPLDs and FPGAs can be used and implemented together for optimum performance and functioning. In these designs, CPLDs are typically dedicated to acting as glue logic and they also boot up the FPGA and the rest of the board.

Choosing a CPLD

You will find a lot of options even within CPLDs when you actually go out to invest in some hardware for your project. When browsing through your options for CPLDs, there are certain salient parameters that you should also keep in the forefront of your mind and use to basically determine what some of the most important features are in your CPLD. your criteria could, of course, vary in accordance with your personal, specific requirements and needs

- Always check the density of the chip and the number I/Os available

- Figure out how great a system performance you require and get a suitable speed grade in your CPLD, otherwise you will end up paying way more than what you actually need and are using in practical application

- Go through the power requirements of the device, standby as well as dynamic, and see if it fits within what you can provide

CPLD FAQ

What is a CPLD?

A: CPLD stands for Complex Programmable Logic Device. It is a type of integrated circuit that can be programmed to perform a variety of logic functions.

How does a CPLD differ from a microprocessor?

A: A microprocessor is a central processing unit (CPU) that performs a wide range of functions, including executing instructions and controlling the operation of a computer or device. A CPLD, on the other hand, is specifically designed for digital logic functions and does not have the processing power or capabilities of a microprocessor.

What are some common uses for CPLDs?

A: CPLDs are commonly used in a variety of applications, including digital logic control, memory decoding, and interface logic. They are also often used in devices such as routers, switches, and automotive systems.

How do I program a CPLD?

A: CPLDs can be programmed using a variety of methods, including using a hardware description language (HDL) such as VHDL or Verilog, or using a graphical programming tool such as Xilinx’s ISE or Altera’s Quartus II software.

Are CPLDs faster than microcontrollers? A: CPLDs are generally faster than microcontrollers at performing logic functions, but they do not have the same processing power or capabilities as a microcontroller.

Can CPLDs be used in place of microcontrollers in certain applications?

A: CPLDs can be used in place of microcontrollers in certain applications where their specific digital logic capabilities are needed. However, microcontrollers are often preferred for their versatility and ability to perform a wider range of functions.

Are CPLDs difficult to use?

A: CPLDs can be somewhat complex to use, especially for those unfamiliar with programming languages or digital logic design. However, there are many resources available to help users learn how to program and use CPLDs, including online tutorials and software tools.

Can CPLDs be used for analog functions?

A: No, CPLDs are specifically designed for digital logic functions and are not suitable for analog functions.

Are CPLDs more expensive than microcontrollers?

A: CPLDs can be more expensive than microcontrollers, depending on the specific features and capabilities of the device. However, CPLDs can also offer cost savings in certain applications due to their ability to perform multiple functions on a single chip.

Are CPLDs still used in modern electronics?

A: Yes, CPLDs are still widely used in modern electronics and continue to be an important component in a variety of applications.