Metastability in FPGAs

06/08/2019, hardwarebee

Metastability in FPGAs is a state that digital electronics systems can find themselves stuck in for a period of time. Normally, in a circuit employing the use of digital logic, the input signal coming into the circuit and being interpreted needs to either fall as a 1 or a 0. Any voltage levels that fall in an intermediate range may not be interpretable or processed by the system and, as a result, cause the logic gates of the circuit to misbehave and persist in an unstable equilibrium state for a given period of time.

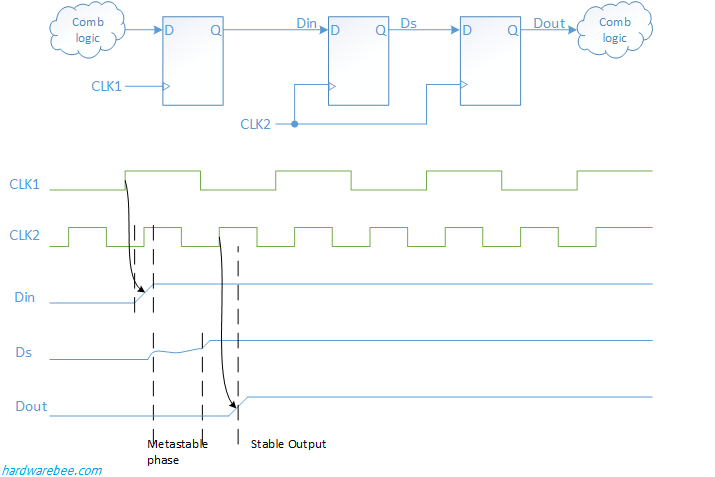

In the following diagram we can see a classic case of metastability in FPGA. There are 3 flip flops in two different clock domains. The first flip flop is sampling a combinatoric-logic with CLK1 and the flip flop output is entering another clock domain – CLK2. The timing diagram below shows the timing relationship between CLK1 and CLK2.

The timing diagram shows how Din is sampled by CLK2 exactly on transition from zero to one, and therefore entering into metastability state.

Metastability is a state in asynchronous digital systems or systems that employ the use of more than one independent clock domains and can cause significant damage in the form of system failure, particularly in FPGAs.

How Does it Work in an FPGA?

As mentioned before, metastability is introduced when the input signals hovers between 1 and 0 while the clock is sampling, meaning the system is unable to derive an output signal for a particular time period. This usually happens when a signal is being transferred from one clock domain to another in a system using multiple, asynchronous clock domains. That is why metastability is not seen or experienced in synchronous systems where the incoming signals are required to meet the register timing requirements all the time and in all cases.

How Metastability Turns into System Failure?

Normally, in many cases, if the system does get stuck in such an unstable equilibrium state, it tends to resolve itself by shifting to a valid state, wither the old or the new value. It must revert back to a valid state before the signal actually reaches the next register. System failure is often the result of the inability of the circuitry to resolve the state of metastability before the input signal reaches the next register.

Preventing Metastability in FPGAs

First and foremost, it’s advised your FPGA design will be utilizing one master clock signal or several clocks derived from this maser clock. The answer to resolving the issue of metastability caused by any reason is to employ what is known as the ‘double flop’ technique on your data. What you do, is that you allow your first flip flop to sample the asynchronous input signal coming from the clock, resulting in the generation of a metastable state. The same output, when again sampled by a second flip flop, will give you a stable condition, thus, resolving the issue of metastability and successfully persevering the integrity of your system and circuitry.

Another way is to, instead of trying to eradicate the presence of metastability altogether, which is quite a difficult thing to do, reduce the Mean Time Between Failures, or the MTBF. The MTBF can be significantly increased using the right methodologies and design modifications, allowing the system to operate for a given length of time without undergoing a spiral into the metastable state and risking the chances of system failure. It is extremely important to detect as well as counter metastable states in FPGAs designs as they may be implemented in critical devices such as medical equipment.