Verilog vs. VHDL – What to Choose?

16/05/2019, hardwarebee

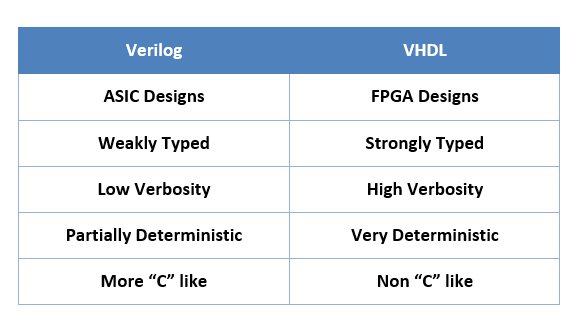

The world of HDL (Hardware Description Language) is divided between Verilog vs VHDL. Some believe that Verilog is best suited for ASIC and FPGA development and some believe that VHDL is a much more superior programing language. This debate has been carrying on since the past few decades. And it does not look likely to stop anytime soon.

In this article we will provide an overview over what separates two of the most prominent languages Verilog vs VHDL. In addition, we will analyze the strengths and weaknesses of both: Verilog and VHDL, to help you make an educated decision regarding which language to use.

What is VHDL?

VHDL stands for VHSIC Hardware Description Language. VHSIC, in turn, stands for Very High-Speed Integrated Circuit. VHDL is based on ADA programming language.

Many people find VHDL to be much more verbose than its counterpart in Verilog and you end up having to write many more lines of code when compared with the other option. However, a major benefit of this verbosity and a non C like syntax is that it flows much more naturally and thus, you may find it relatively easy to use. So, while you may find that the code written with VHDL as the programming language is longer and takes up more space, it also tends to flow better and is easier to understand as you read it.

VHDL is strongly typed, which means that you need to be very careful when typing the code as every character that you put in as input must match accurately with the defined data types. In the case that you end up mixing data types or make a mistake in your code writing, you will receive a compiler error.

VHDL may not be the perfect choice when it comes to low level modelling as it does not possess the same customizable features for a basic set of logic gates which can be used to run simulations. That doesn’t mean that VHDL does not support low level hardware modelling at all; it simply means that Verilog is the better option to go for in such a case.

On the other hand, VHDL is designed in a way that makes it much better than Verilog in the aspect of high-level hardware modelling. This is specially aided by the fact that VHDL supports numerous types of data types including those that are predefined by the language itself as mentioned before, as well as user defined data types which introduces the concept of customizability and flexibility. This allows you to create complex high-level hardware systems with much more ease.

VHDL also has a library management system which contains compiled architectures, packages, as well as configurations which can be accessed by the user on top of the code. This simplifies the process of creating complex hardware systems in FPGA.

Read about VHDL history on this page.

The following is an example of a VHDL 8 bit count:

entity up_counter is

port (

cout :out std_logic_vector (7 downto 0); — Output of the counter

enable :in std_logic; — Enable counting

clk :in std_logic; — Input clock

reset :in std_logic — Input reset

);

end entity;

architecture rtl of up_counter is

signal count :std_logic_vector (7 downto 0);

begin

process (clk, reset) begin

if (reset = ‘1’) then

count <= (others=>’0′);

elsif (rising_edge(clk)) then

if (enable = ‘1’) then

count <= count + 1;

end if;

end if;

end process;

cout <= count;

end architecture;

What is Verilog?

Verilog is more compact and to the point — asking you to write only a few lines of code as opposed to VHDL which demands you to write more lines. As a result, the verbosity is relatively low. Unlike VHDL, it is much more similar to the C language and shares some of the syntax. It also has a decreased number of predefined programming constructs.

So, with Verilog, you need to have a good understanding of the compact characters and terms utilized by the language and it will reward you with fewer and shorter lines of code. As opposed to VHDL, Verilog is much more loosely typed and allows you to mix and match data types.

Verilog is much better suited if you are looking to model at the low level. The reason behind this is that Verilog was initially created for the sole purpose of modelling and simulating logic gates which is why it has special functions to allow you to run basic primitive simulations using Verilog code to determine what will happen in a given scenario. Verilog also allows you to define your own primitives, a feature called user-defined primitives.

On the flip side, Verilog is not as suited for high level hardware modelling when compared to VHDL as it does not support complex data types but rather only delves in the simpler ones. Add to that the fact that users are not allowed to define their own data types in this language, and it further proves that VHDL is the way to go in this aspect. Verilog also does not support library management.

Read about Verilog history on this page.

An example for 8 bit up counter implementation using Verilog:

module up_counter_8bit (out, enable, clk, clock Input, reset);

output [7:0] out;

input enable,

clk, reset;

reg [7:0] out;

always @(posedge clk)

if (reset) begin

out <= 8’b0 ;

end else if (enable) begin

out <= out + 1;

end

endmodule

Verilog vs. VHDL Conclusion

At the end of the day, it is advised that you dabble in and practice with both Verilog and VHDL at some point in your life as you are bound to encounter them in this field. The best idea is to code using them yourself practically and practice each of the languages to determine which one works best for you.